Weeroc has designed several analogue and mixed signal IP blocks in Microchip ATMX150RHA technology with support of CNES. These IP blocks has been tested for electrical performances, temperature variation and irradiation up to 100krad.

The test vehicle is composed of:

- Two different kind of bandgap

- A 10-bit 10MHz SAR ADC

- A 500MHz-bandwidth switch

One bandgap is a low surface trimmable...

In contrast to a pure digital ASIC design flow, which is highly regarded as a top-down design methodology, building an analog mixed-signal complex function usually requires a bottom-up design approach. The latter is based traditionally on a full custom design approach where each functional analog block, after it has been individually designed and verified, it is integrated at a higher level to...

The PROMISE project gathers IC experts from 7 European institutions. This project has received funding from the European Union’s Horizon 2020 research and innovation program under grant agreement No 870358. It was launched in early 2020 and is planned to run for the next 3 years. PROMISE stands for PROgrammable MIxed Signal Electronics. It’s tailored to bring a flexible mixed-signal ASIC...

This brief presents the experience of integrating two high-performance Data Converter IPs, an ADC and a DAC, in a single rad-hard test-chip. A system-level perspective is taken, underlining the importance of Design-for-Testability (DfT) structures and tuning structures for debugging purposes and achieving first-time right silicon.

Modeling the interactions between domains (PCB, package,...

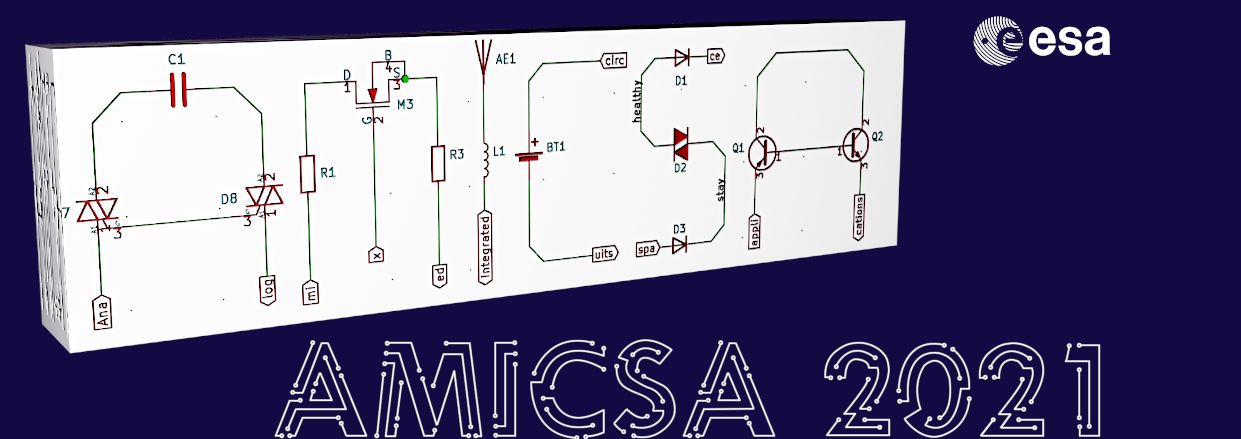

The MAS-FE (Adaptable Scalable Mixed-Signal Sensor/Actuator Front-End for Micro-C and FPGAs) project, funded by ESA, has reached post-silicon status and an ASIC testchip is currently being validated and characterized. The MAS-FE original concept is that of a space-capable, high performance, flexible front-end ASIC in the 10-100Mps segment that can interface effectively between the analogue...